NVIDIA在IEDM大会展示对下一代AI加速器的设计概念愿景,其中有两项重点:硅光子(SiPh)与3D记忆体堆叠;NVIDIA于IEDM介绍下一代加速器的愿景时,就提到将利用SiPH取代现行的电通讯作为大型运算GPU的中介层。

SiPh硅光子是采用光通讯的技术,相较现行的电通讯方式具备更高的频宽与更低的延迟,同时也更为省电;除了作为中介层以外,NVIDIA也在新GPU晶片计画利用SiPh作为连接多个晶粒的通讯技术,使多个GPU晶粒之间能够以更高速、低延迟的通道连接与互通。

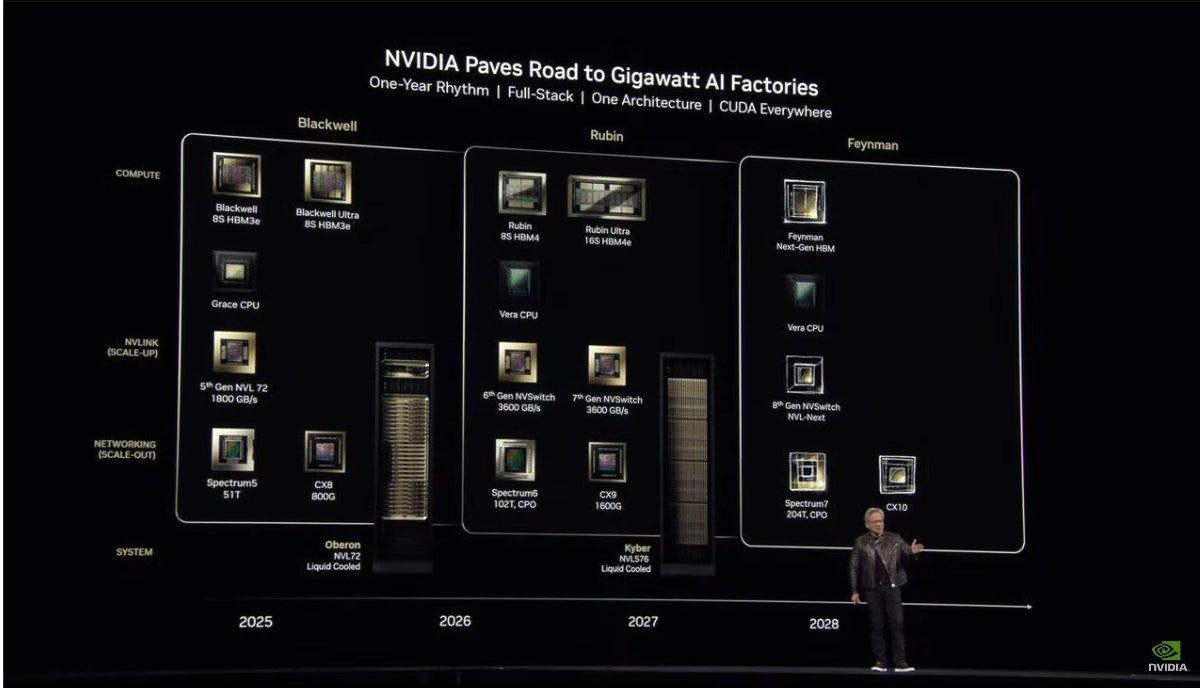

Here's @NVIDIA's vision of the future of AI compute.

— 𝐷𝑟. 𝐼𝑎𝑛 𝐶𝑢𝑡𝑟𝑒𝑠𝑠 (@IanCutress) December 8, 2024

Silicon photonics interposer

SiPh intrachip and interchip

12 SiPh connects, 3 per GPU tile

4 GPU tiles per tier

GPU 'tiers' (GPU on GPU?!?)

3D Stacked DRAM, 6 per tile, fine-grained

From #iedm24. My guess, 2028/2029/2030… pic.twitter.com/5IsDkYSWT2

此外,NVIDIA也计画使用3D堆叠建构下一代AI加速器,包括垂直堆叠多个GPU晶粒,借此缩减晶片面积与提高密度;NVIDIA将此技术称为GPU Tier(GPU层),每个GPU Tier由4个GPU晶粒以垂直方式堆叠,每个GPU晶粒分配3路的SiPh进行相互连接,同时还计画把记忆体也一併利用3D堆叠至晶片内,每个晶粒将配有6个记忆体颗粒。

不过这样的技术还不会在2025年现身,产业分析师Ian Cutress认为从整个晶片概念评估,并考虑到SiPh的量产,还要考虑多层3D堆叠的大型晶粒势必带来的发热等问题,比较可能实作的时间点会在2028年至2030年左右。

发表评论 取消回复